计算机系统的层次结构

系统复杂性管理的方法1

抽象

系统复杂性管理的方法2(3Y)

层次化(Hierachy):将被设计的系统划分为多个模块和子模块

模块化(Modularity):有明确定义的功能和接口

规则性(Regularity):模块更容易被重用

冯诺伊曼计算机的特点

计算机由五大部件组成(存储器,控制器,运算器,输入设备,输出设备)

指令和数据以同等地位存于存储器,可按地址访问

指令和数据用二进制表示

指令由操作码和地址码组成

存储程序

以运算器为中心

运算器的组成

运算单元(ALU)

输入数据寄存器(ACC和X)

额外数据寄存器(MQ)

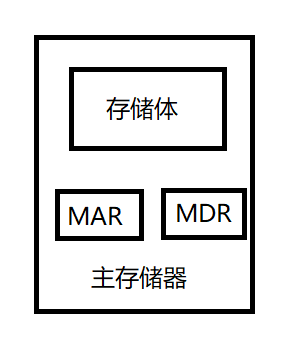

存储器的基本组成

MAR:存储器地址寄存器(反应存储单元的个数)

MDR:存储器数据寄存器(存储器数据寄存器反映存储字长)

存储体—存储单元—存储元件

存储单元:存放一串二进制代码

存储字:存储单元中二进制代码的组合

存储字长:存储单元中二进制代码的位数,每个存储单元赋予一个地址

按地址寻访

控制器的功能

解释指令

保证指令的按序执行

完成一条指令

- 取指令 PC(存放当前欲执行指令的地址,具有计数功能PC+1=PC)

- 分析指令 IR(存放当前欲执行的指令)

- 执行指令 CU

计算机硬件的主要技术指标

- 机器字长:CPU一次能处理数据的位数,与CPU中的寄存器位数有关

运算速度

- 主频

- 核数,每个核支持的线程数

- 吉普森法

- CPI 执行一条指令所需时钟周期数

- MIPS 每秒执行百万条指令

存储容量

存放二进制信息的总位数

硬件技术对计算机更新换代的影响

时间 硬件技术

1946-1957 电子管

1958-1964 晶体管

1965-1971 中小规模集成电路

1972-1977 大规模集成电路

1978-现在 超大规模集成电路

微型计算机的出现和发展

微处理器芯片 1971

存储器芯片 1970

芯片集成度的提高受以下三方面的限制

- 芯片集成度受物理极限的制约

- 按几何级数递增的制作成本

- 芯片的功耗,散热,线延迟

总线的基本概念

什么是总线?

总显示连接各个部件的信号传输线,是各个部件共享的传输介质

总线上信息的传递

串行:一条数据线

并行:多条数据线

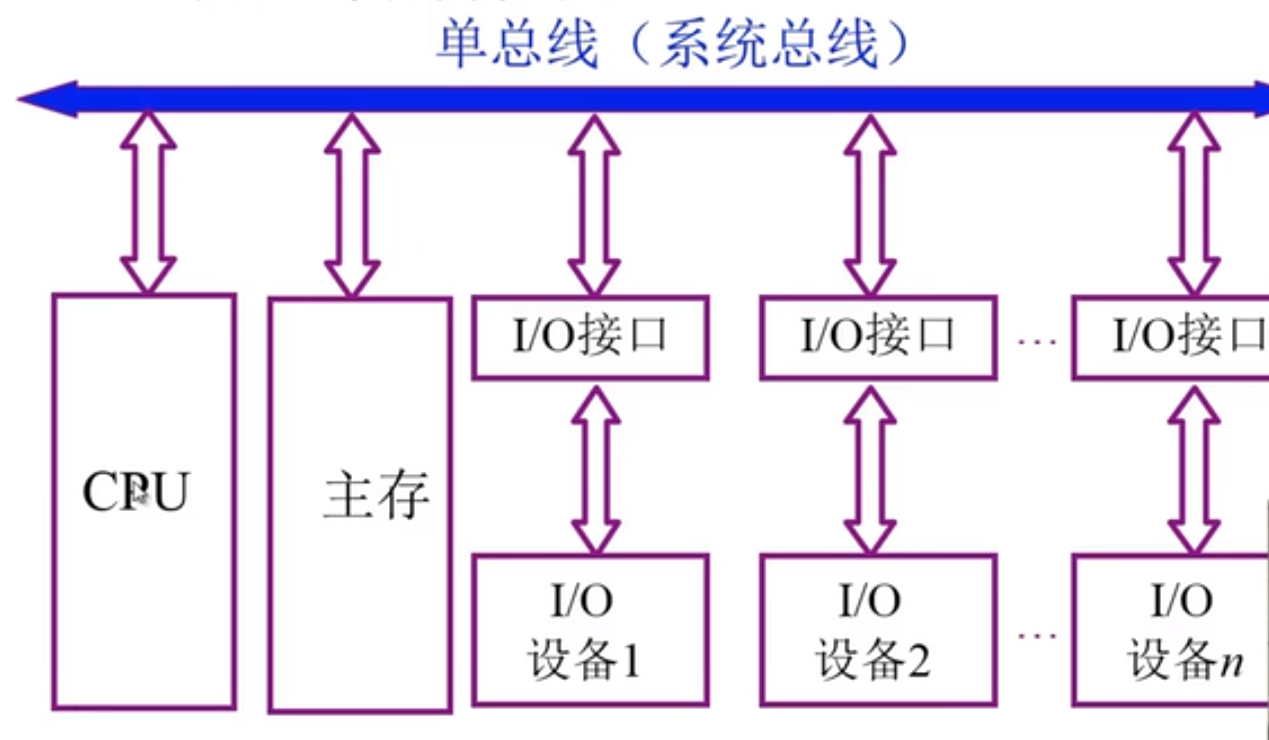

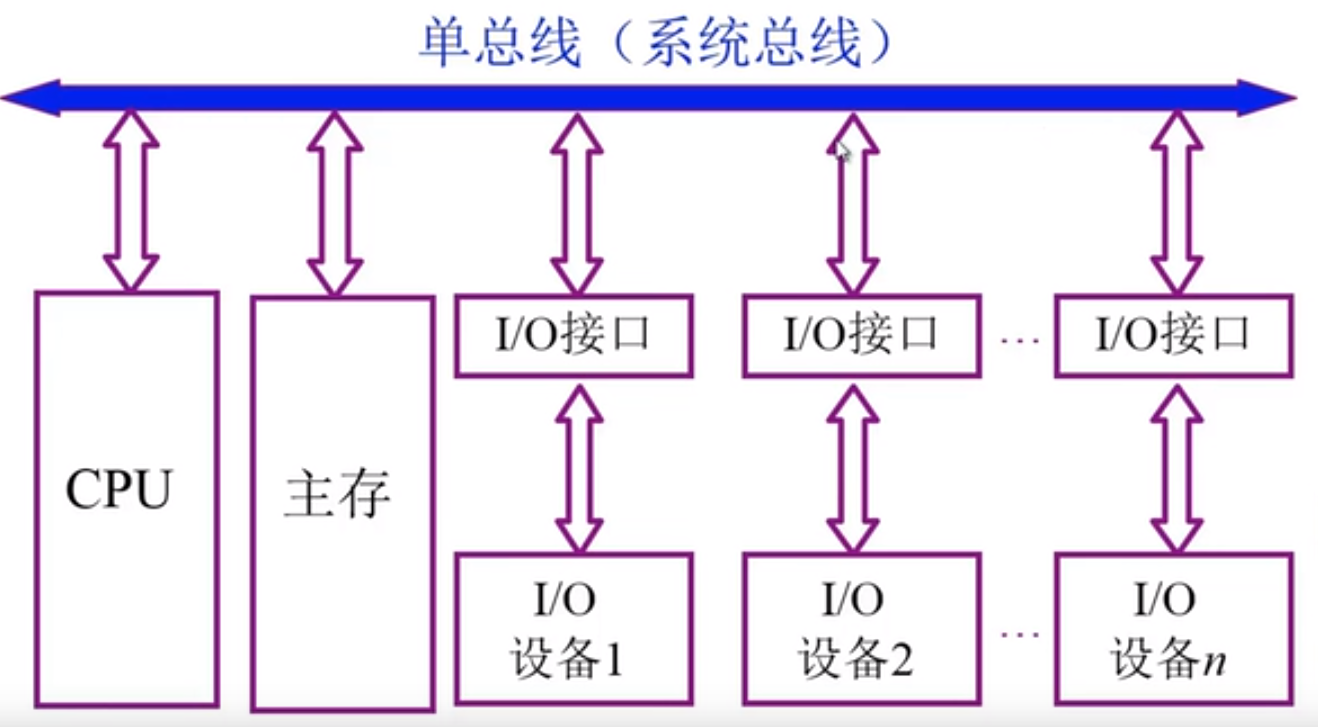

单总线结构框图

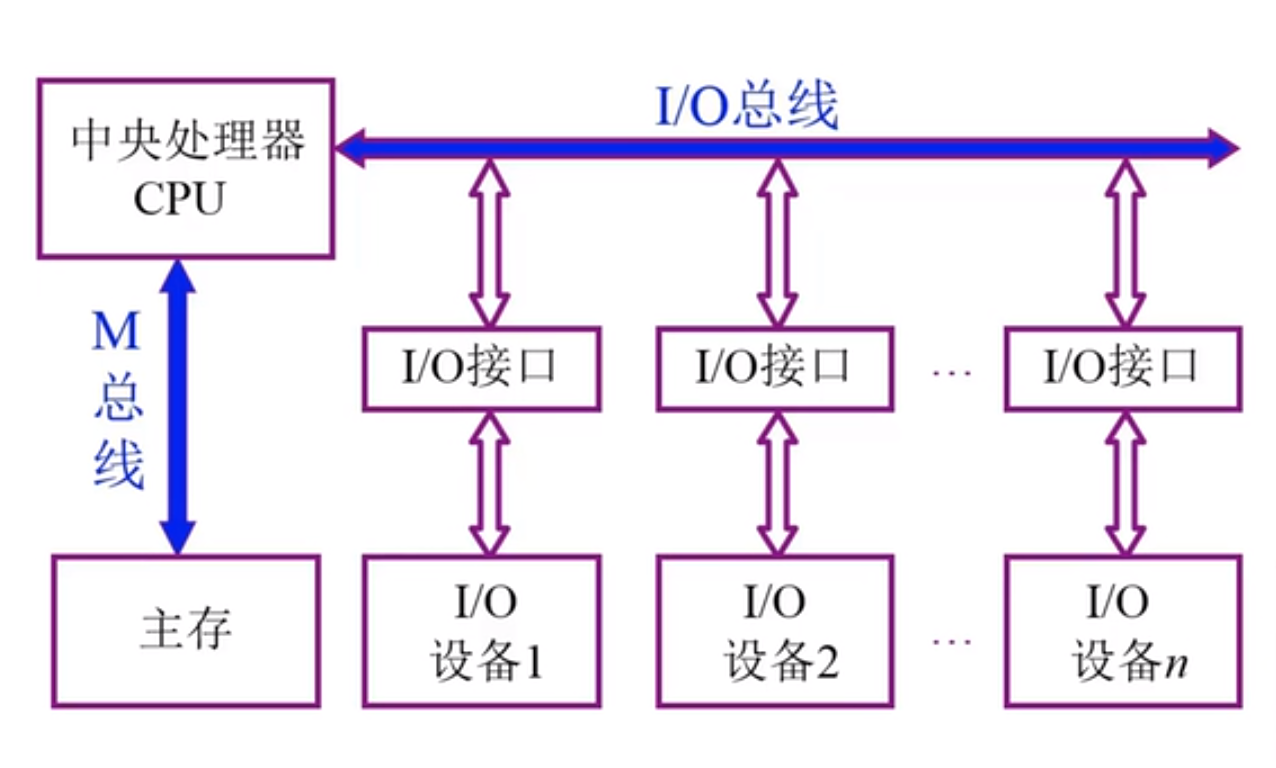

面向CPU的双总线结构框图

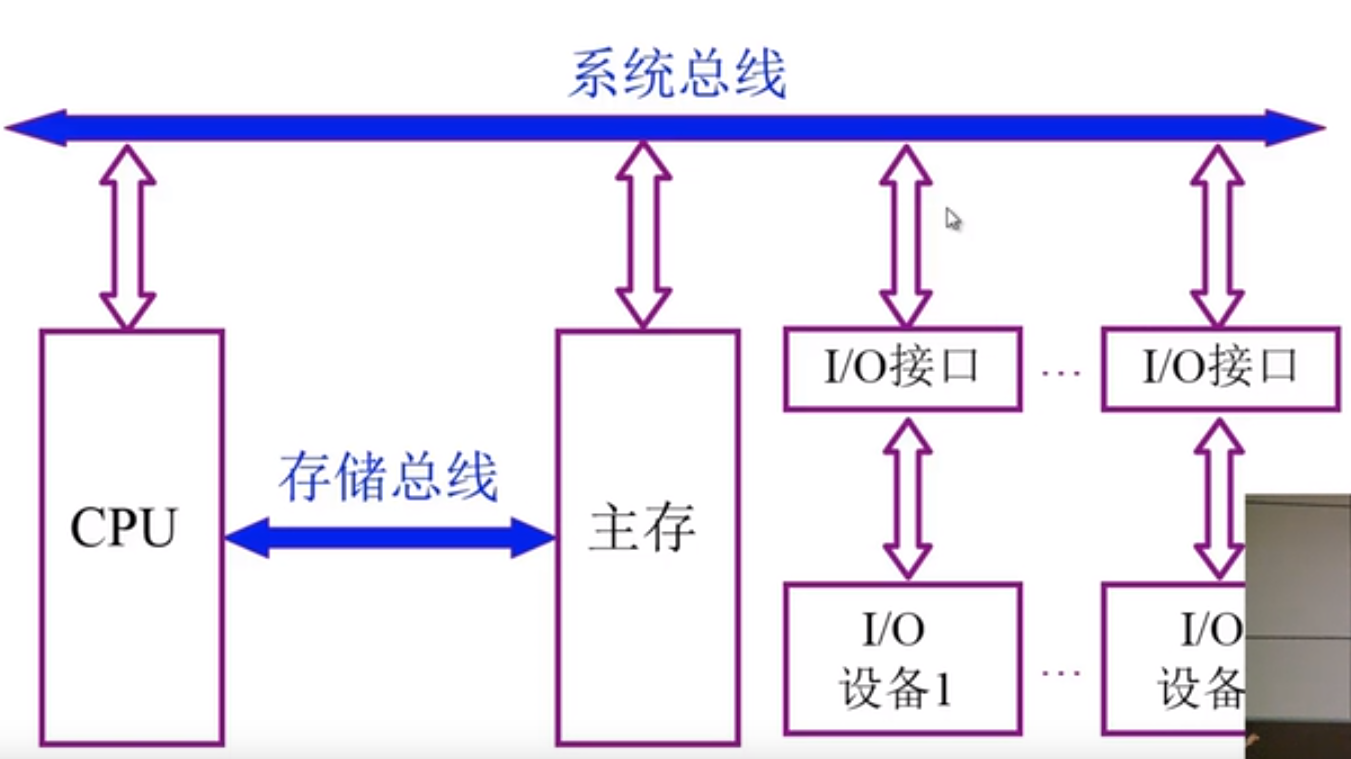

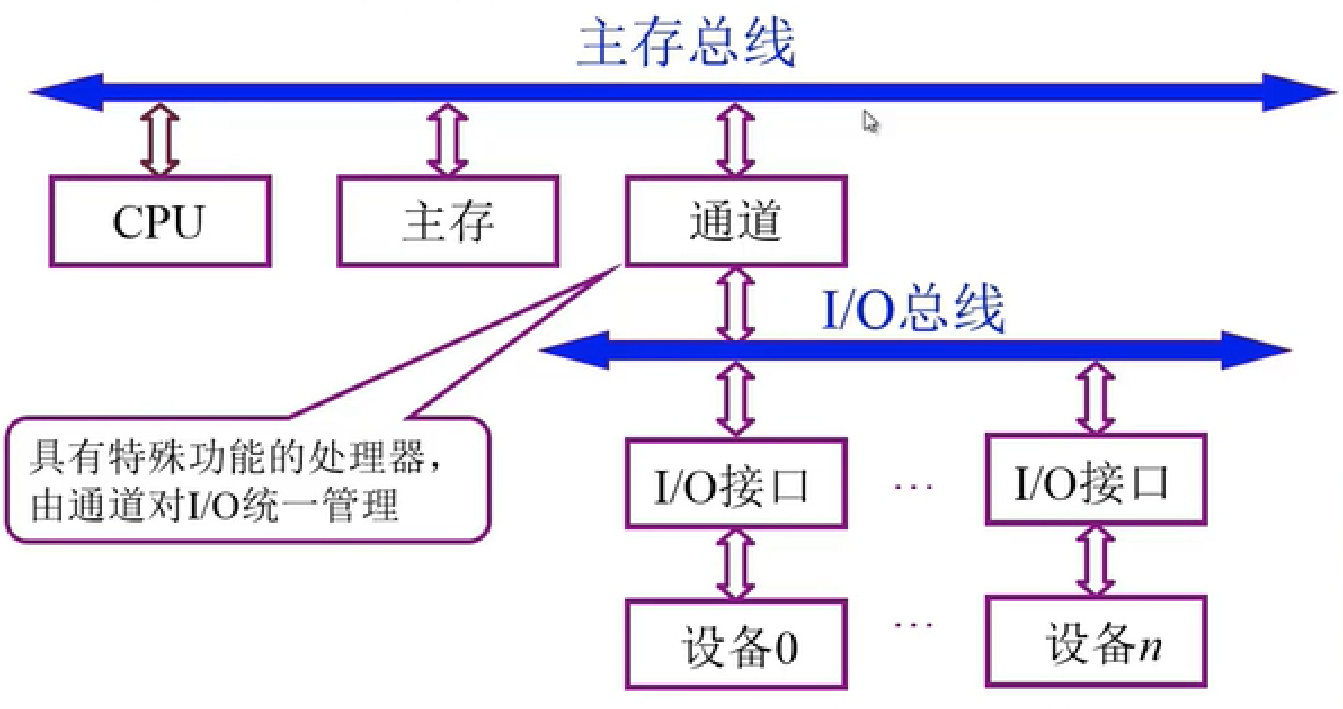

以存储器为中心的双总线结构框图

总线的分类

1:片内总线 芯片内部的总线

2:系统总线 计算机各部件之间的信息传输线

- 数据总线 (双向 与机器字长,存储字长有关)

- 地址总线 (单向 与存储地址,I/O地址有关)

- 控制总线 (有出 有入)

3:通信总线

用于计算机系统之间或计算机系统与其他系统(如控制仪表,移动通信等)之间的通信

- 串行通信总线

- 并行通信总线

总线特性及性能指标

总线特性

- 机械特性 尺寸,形状,管脚数及排列顺序

- 电气特性 传输方向和有效的电平范围

- 功能特性 每根传输线的功能(如地址,数据,控制)

- 时间特性 信号的时序关系

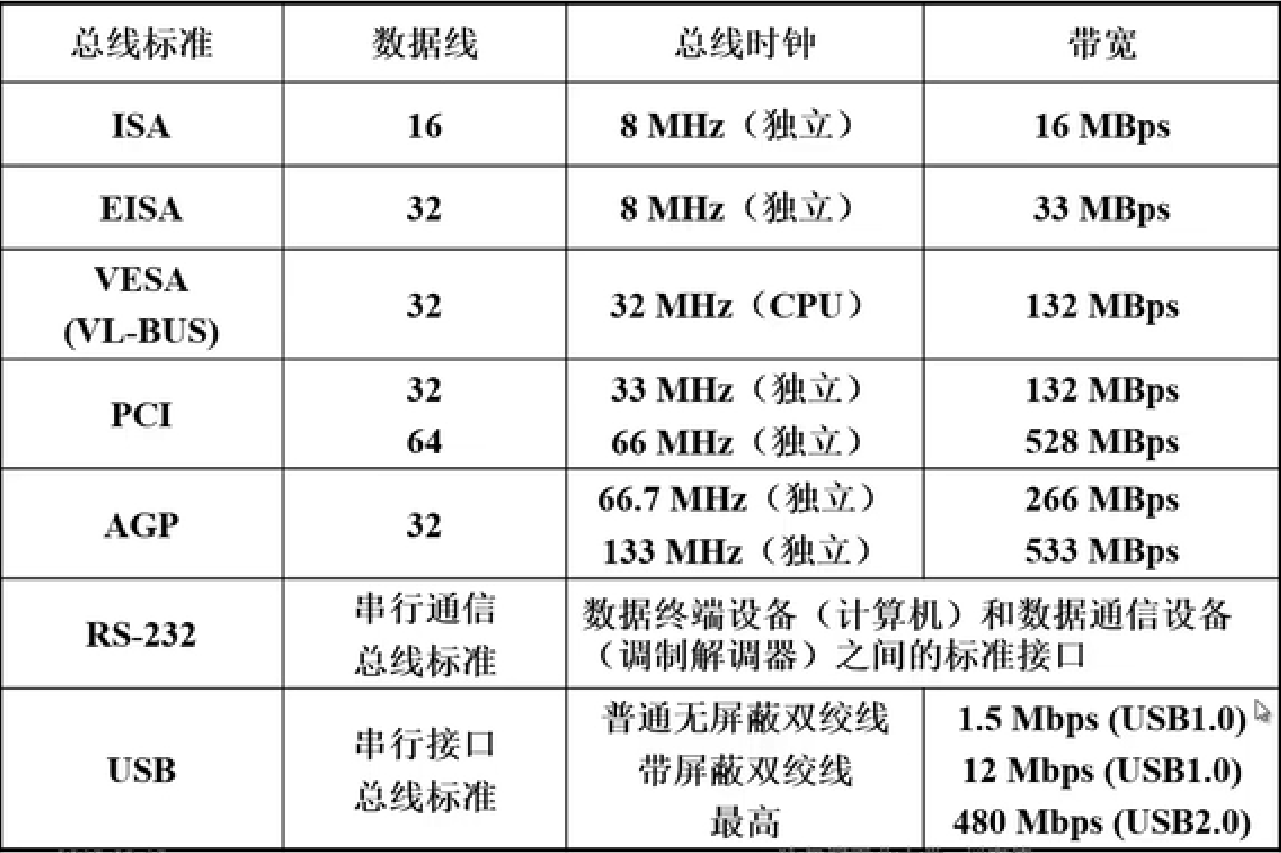

总线的性能指标

- 总线宽度 (数据线的根数)

- 标准传输率 (每秒传输的最大字节数(MBps))

- 时钟同步 (异步 同步,不同步)

- 总线复用 (地址线与数据线复用)

- 信号线数 (地址线,数据线和控制线的总和)

- 总线控制方式 (突发,自动,仲裁,逻辑,计数)

- 其他指标 (负载能力)

总线标准

总线结构

单总线结构

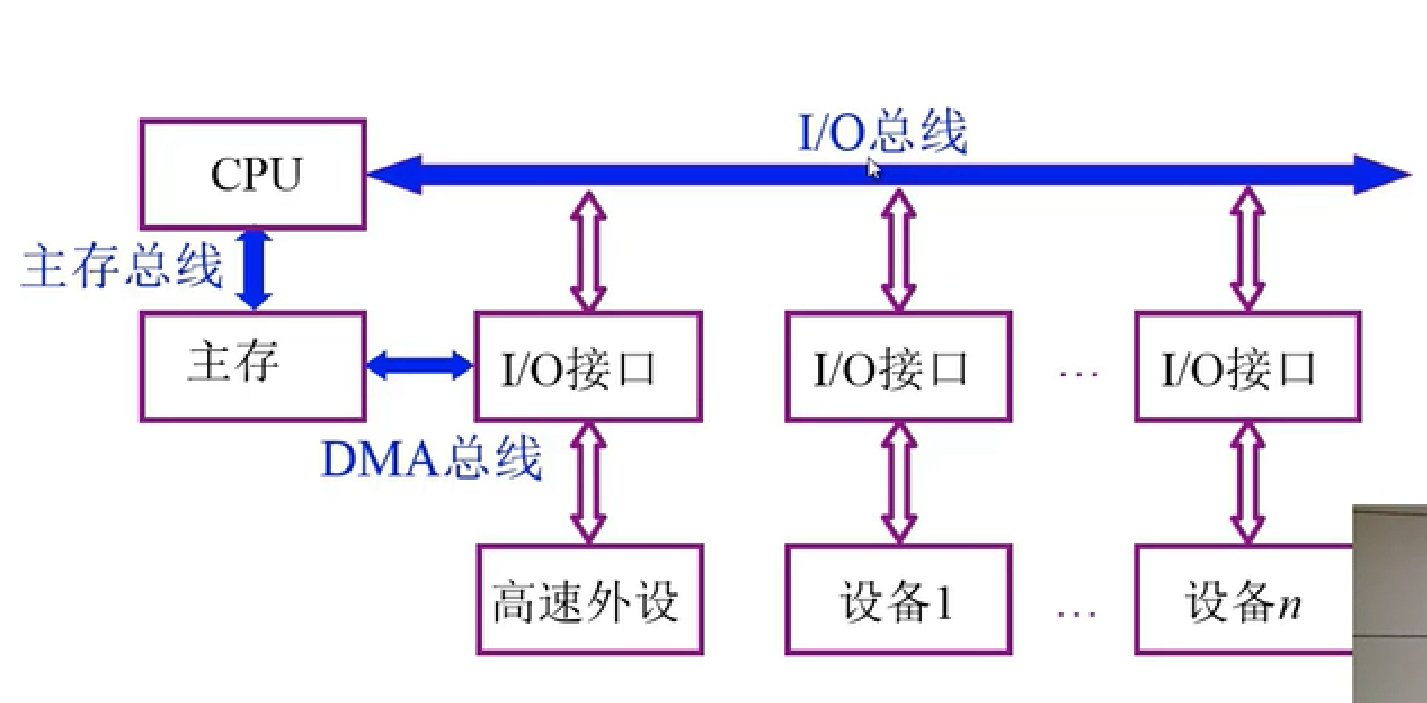

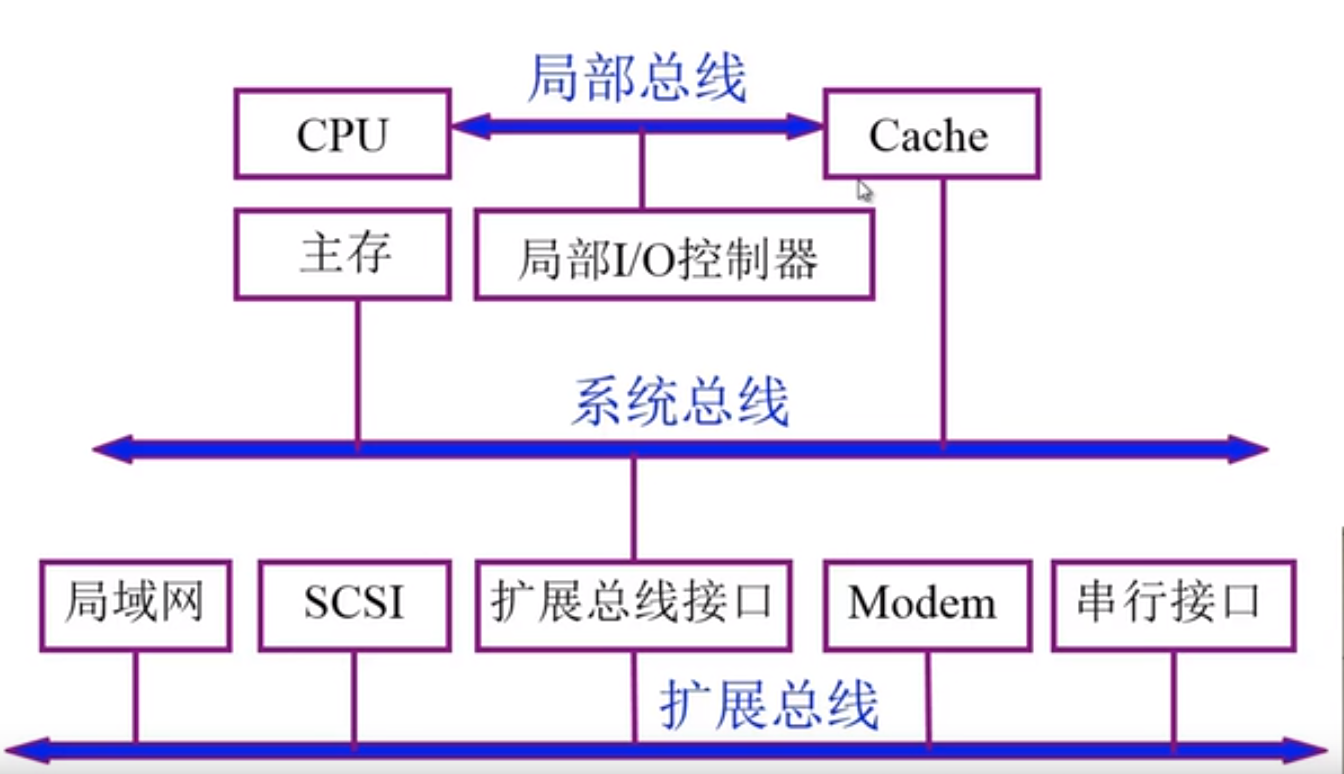

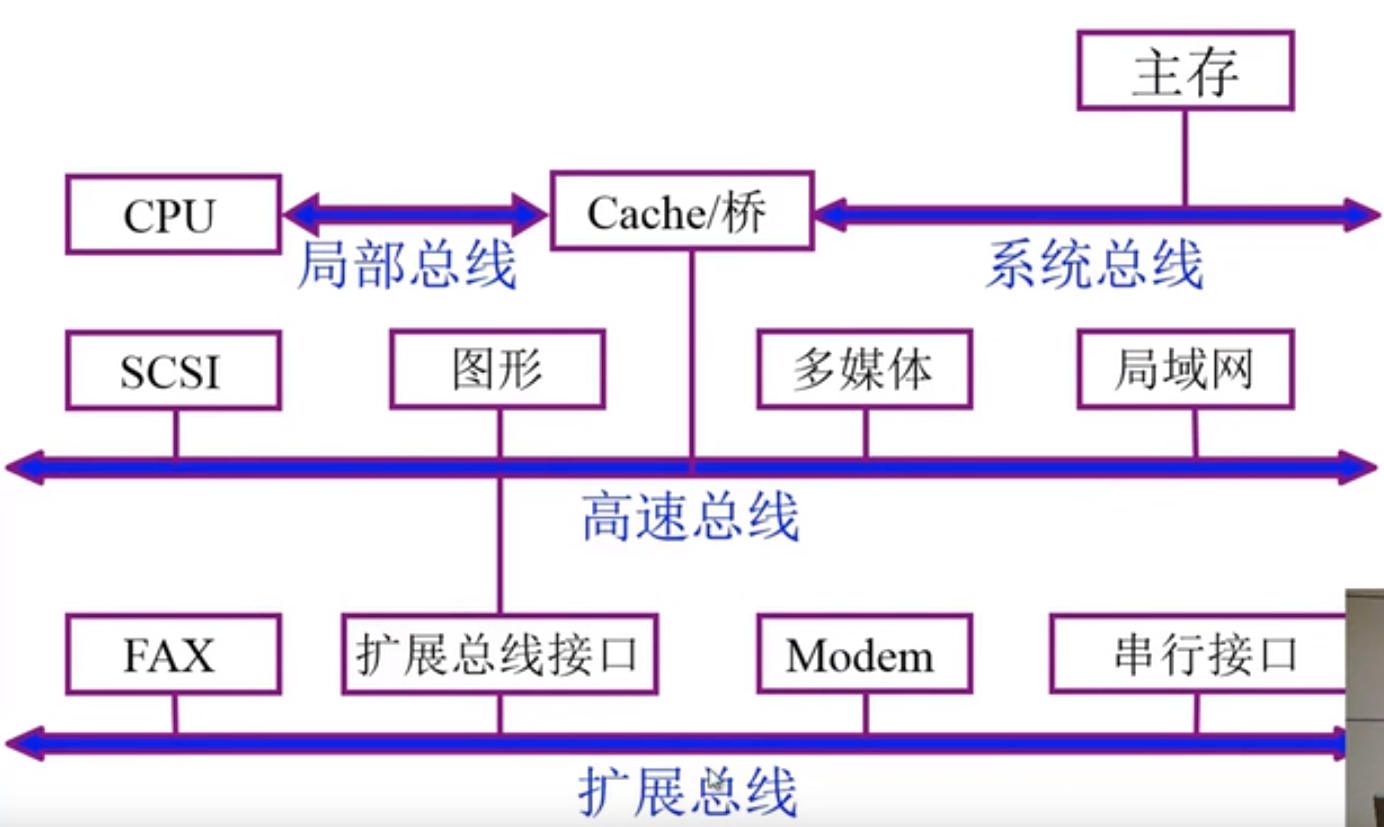

多总线结构

双总线结构

三总线结构

三总线结构另一种形式

四总线结构

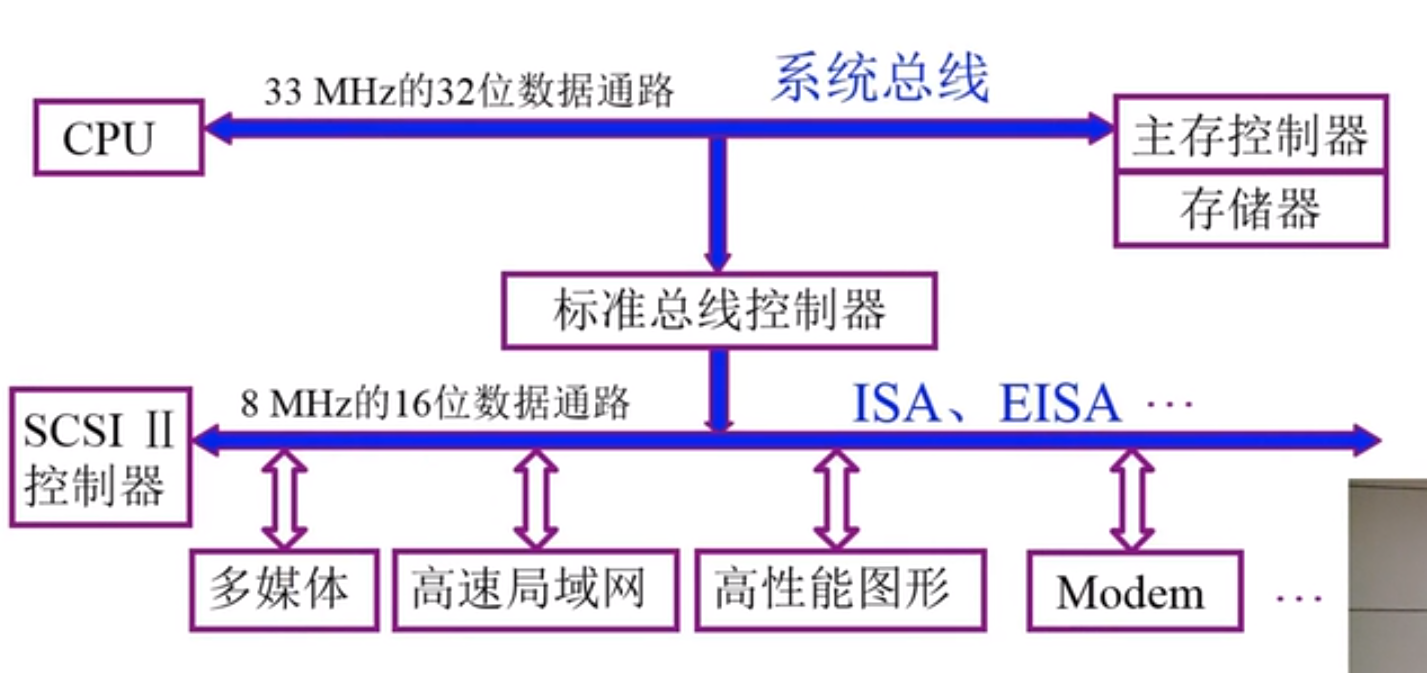

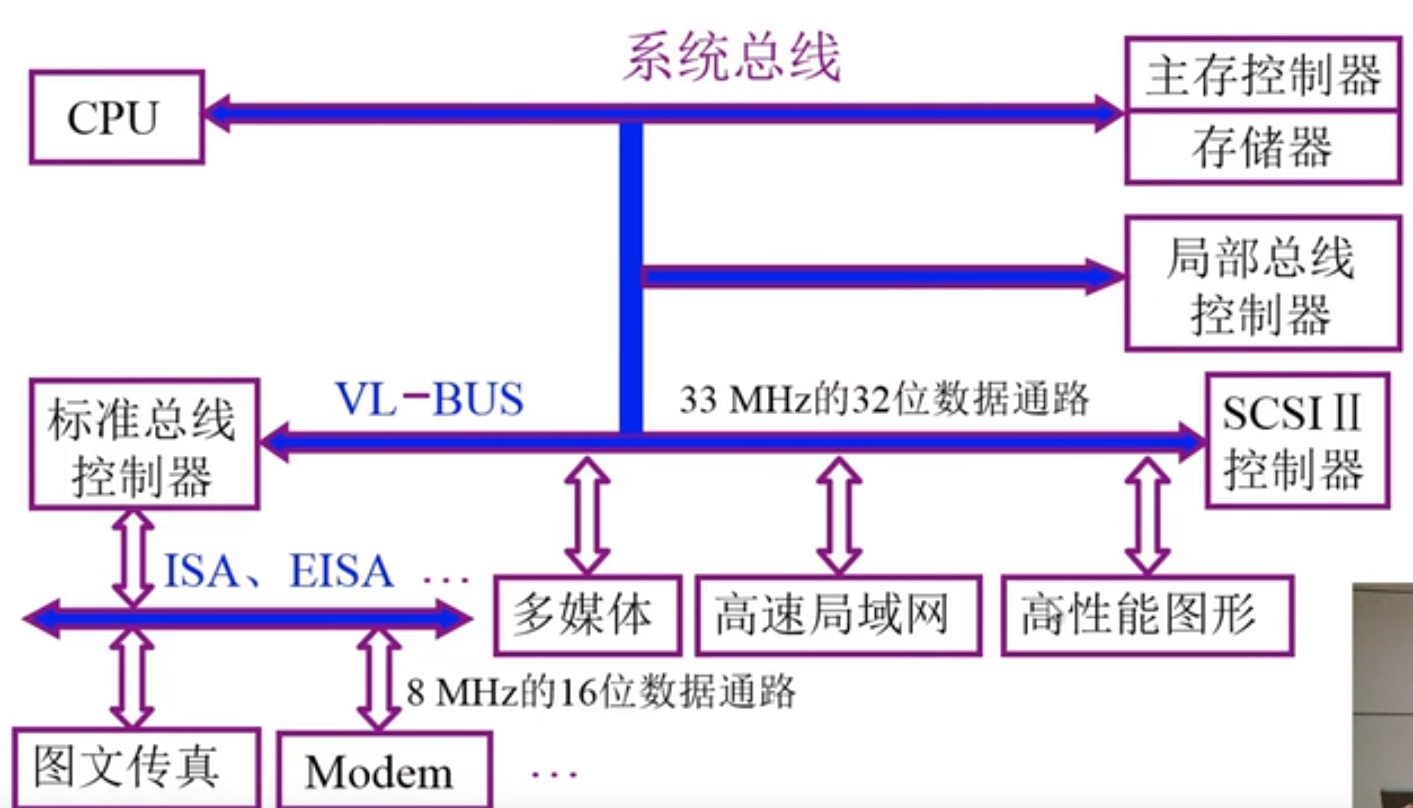

总线结构举例

传统微型机总线结构

VL-BUS局部总线结构

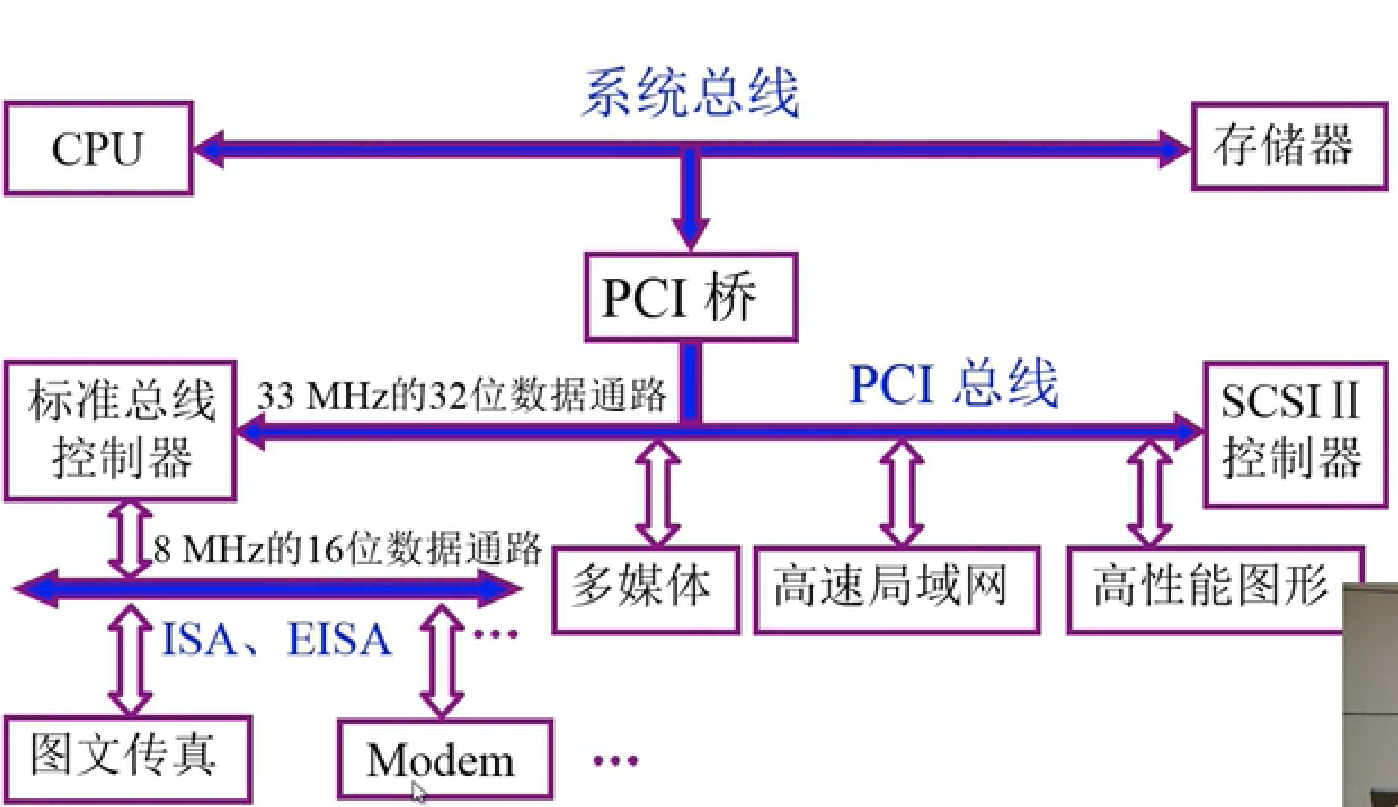

PCI总线结构

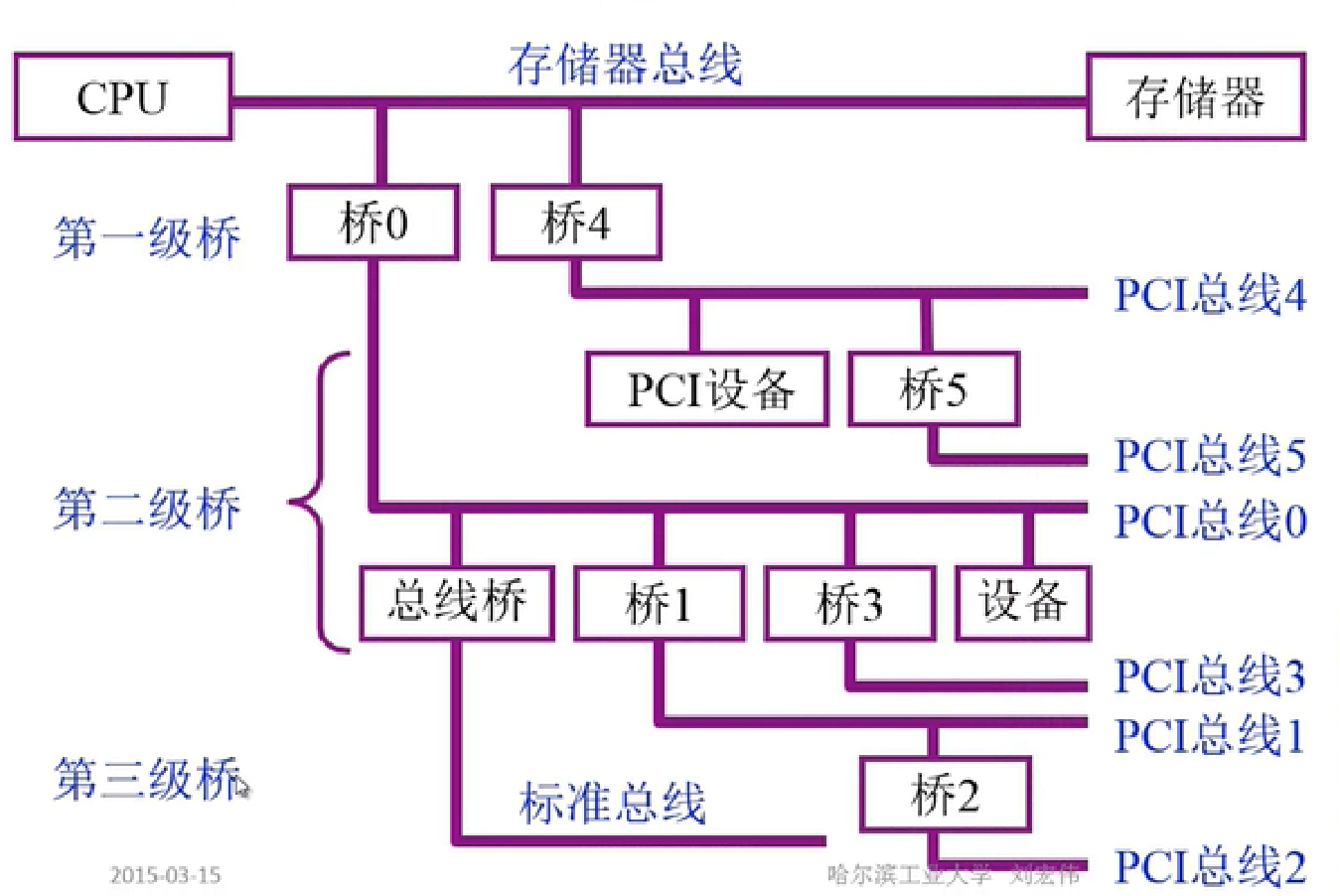

多层PCI总线结构

总线控制

总线判优控制

根据是否能提出总线请求将总线上的设备分为两类

- 主设备(或者是主模块)对总线有控制权

- 从设备(或者是从模块)响应从主设备发来的总线命令

总线判优控制

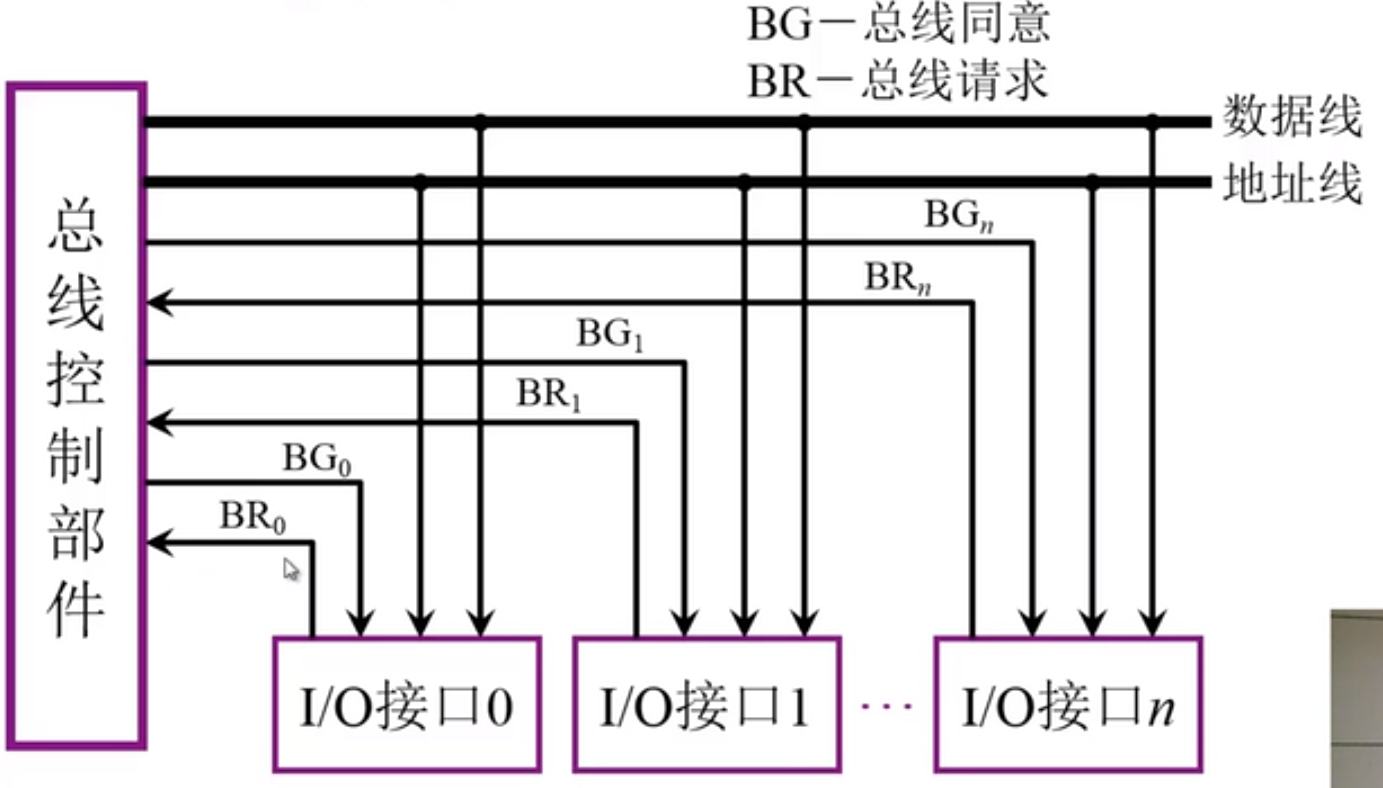

- 集中式(链式查询,计数器定时查询,独立请求方式)

- 分布式

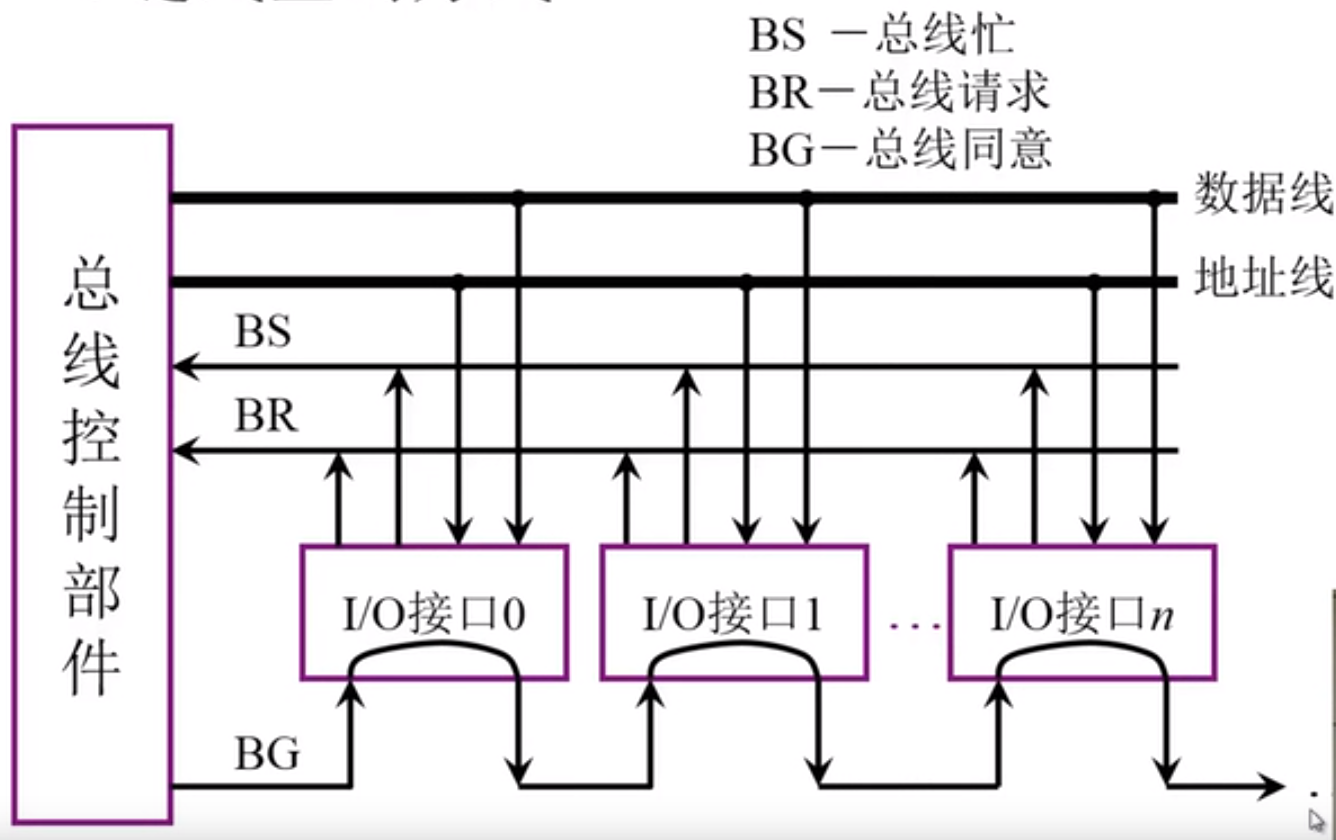

链式查询方式

电路控制结构

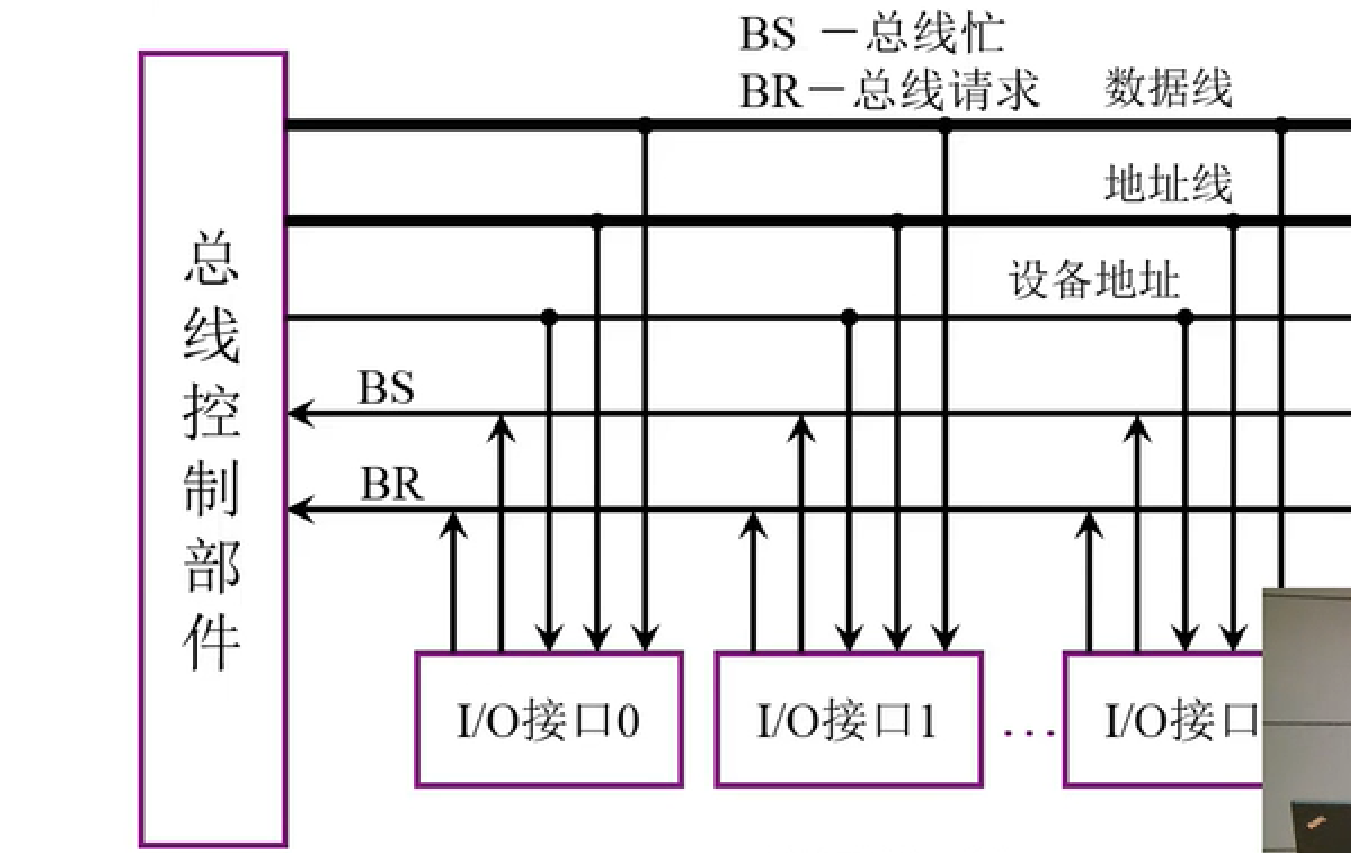

计数器定时查询方式(总线控制部件中有一个计数器)

电路控制结构

独立请求方式(总线控制部件内部有一个排队器)

电路控制结构

总线通信控制

1 目的:解决通信双方协调配合问题

2 总线传输周期

- 申请分配阶段 (主模块申请,总线仲裁决定)

- 寻址阶段 (主模块向从模块给出地址和命令)

- 传数阶段 (主模块和从模块交换数据)

- 结束阶段 (主模块撤消有关信息)

总线通信的四种方式

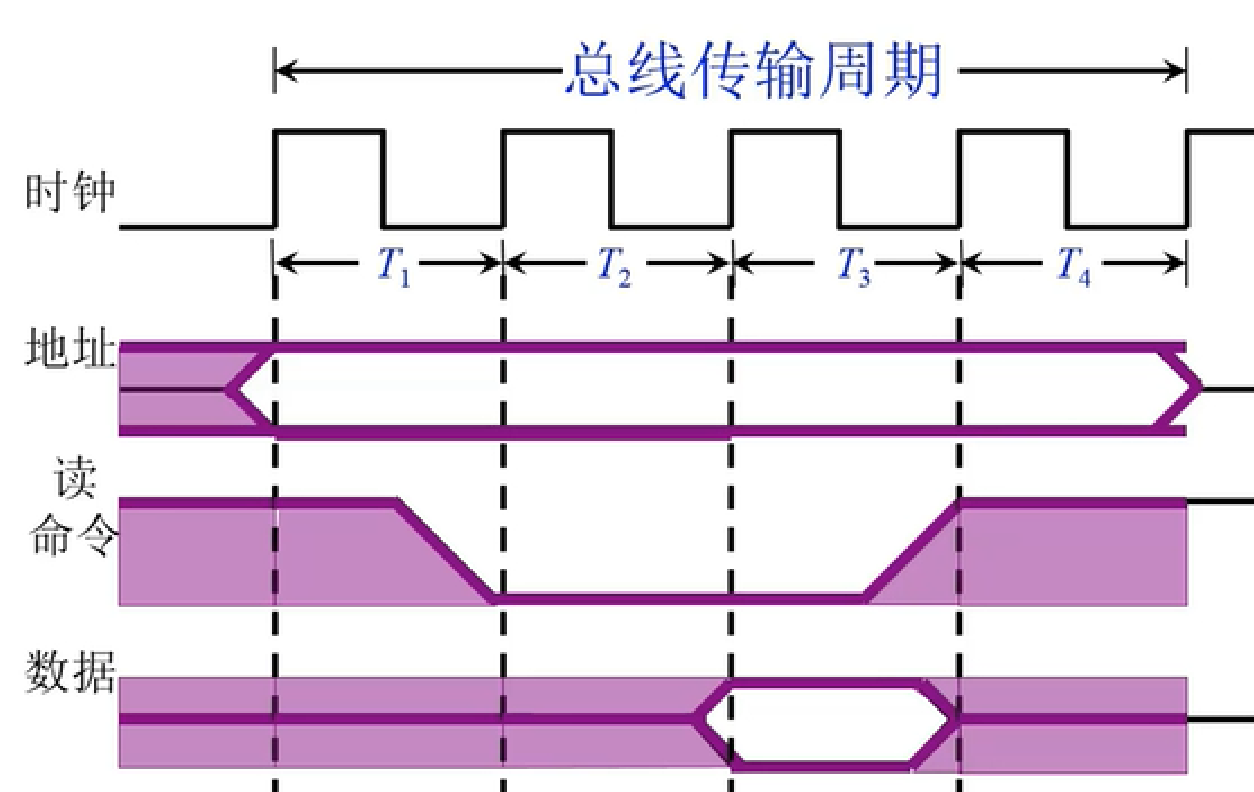

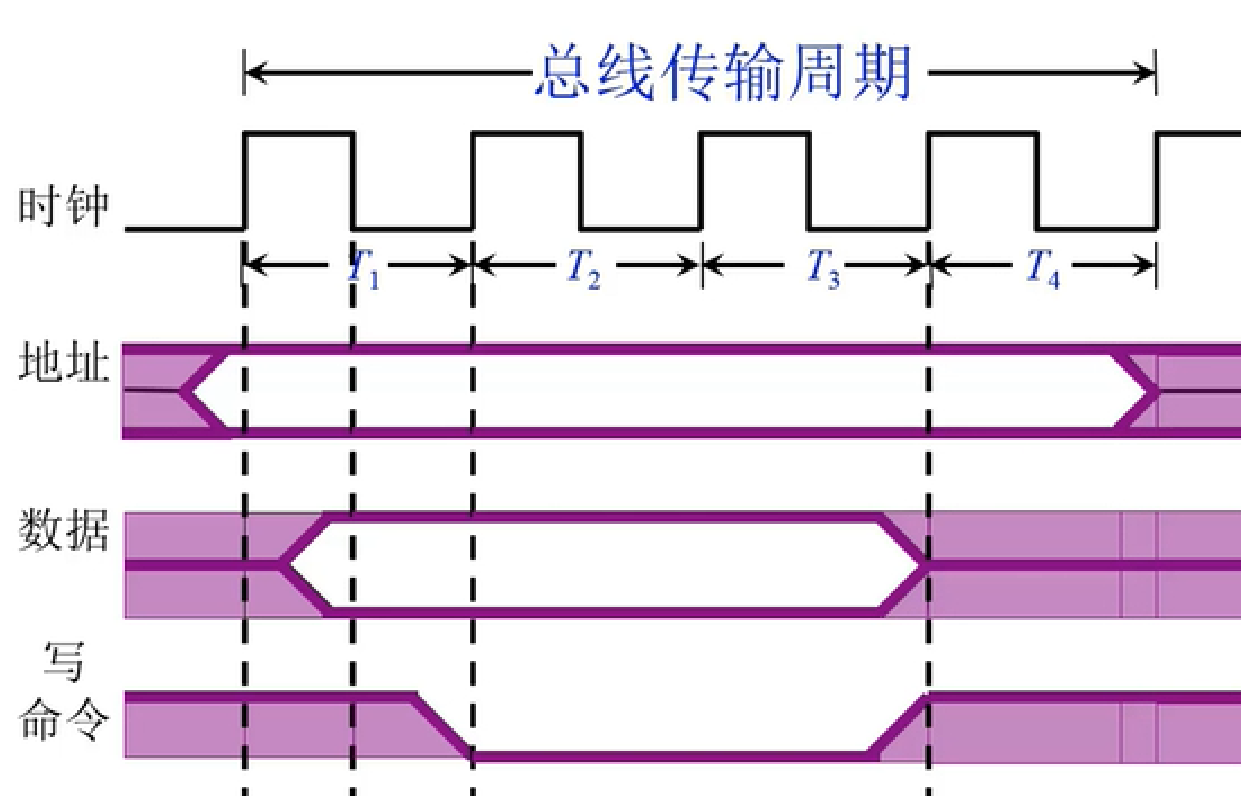

- 同步通信(由统一时标控制数据传送)

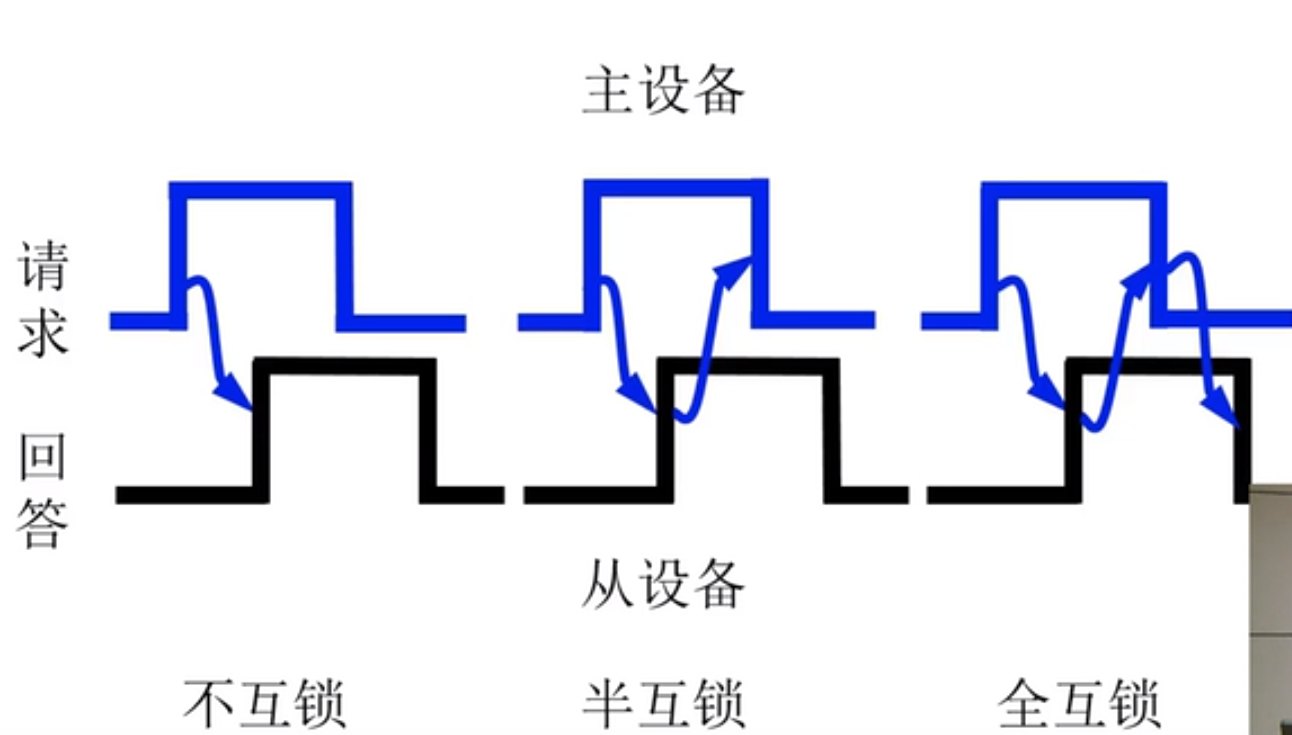

- 异步通信(采用应答方式,没有公共时钟标准)

- 半同步通信(同步,异步结合)

- 分离式通信(充分挖掘系统总线每个瞬间的潜力)

同步式数据输入

同步式数据输出

异步通信

半同步通信(同步,异步结合)

同步:发送方用系统时钟前沿发信号,接收方用系统时钟后沿判断,识别

异步:允许不同速度的模块和谐工作,增加一条等待响应信号 WAIT

一个总线传输周期(以输入数据为例)

- 主模块发地址,命令(占用总线)

- 从模块准备数据(不占用总线,总线空闲)

- 从模块向主模块发数据(占用总线)

分离式通信

充分挖掘系统总线每个瞬间的潜力

一个总线传输周期

- 子周期1:主模块申请占用总线,使用完后即放弃总线的使用权

- 子周期2:从模块申请占用总线,将各种信息送至总线上

分离式通信特点

1:各模块有权申请占用总线

2:采用同步方式通信,不等对方回答

3:各模块准备数据时,不占用总线

4:总线被占用时,无空闲

存储器分类

- 按存储介质分类

- 半导体存储器(TTL,MOS)易失性

- 磁表面存储器(磁头,载磁体)非失性

- 磁芯存储器(硬磁材料,环状元件)非失性

- 光盘存储器(激光,磁光材料)非失性

- 按存取方式分类

- 存取时间与物理地址无关(随机访问)

- 随机存储器(在程序的执行过程中可读可写)

- 只读存储器(在程序的执行过程中只读)

- 存取时间与物理地址有关(串行访问)

- 顺序存取存储器(磁带)

- 直接存取存储器(磁盘)

- 存取时间与物理地址无关(随机访问)

- 按在计算机中的作用分类

- 主存储器

- RAM(静态RAM,动态RAM)

- ROM(MROM,PROM,EPROM,EEPROM)

- Flash Memory

- 高速缓冲存储器(Cache)

- 辅助存储器(磁盘,磁带,光盘)

- 主存储器

主存的技术指标

存储容量(主存存放二进制代码的总位数)

存储时间

- 存储时间(存储器的访问时间,读出时间,写入时间)

- 存取周期(连续两次独立的存储器操作所需要的最小时间间隔,读周期,写周期)

- 存储器的带宽(位/秒)

动态RAM和静态RAM的比较

| DRAM | SRAM | |

|---|---|---|

| 存储原理 | 电容 | 触发器 |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少 | 多 |

| 功耗 | 小 | 大 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 有 | 无 |

只读存储器(ROM)

- 掩模ROM(MROM)

- PROM(一次性编程)

- EPROM(多次性编程)

- EEPROM(多次性编程)

- FLASH Memory(闪存型存储器)

存储器与CPU的连接

- 地址线得连接

- 数据线的链接

- 读/写命令线的连接

- 片选线的连接

- 合理选择存储芯片

- 其他 时序,负载

存储器的校验

编码的最小距离

任意两组合法代码之间二进制位数的最小差异

编码的纠错,检错能力与编码的最小距离有关

L-1=D+C(D>=C)

L——编码的最小距离

D——检测错误的位数

C——纠正错位的位数

汉明码的组成

- 汉明码采用奇偶校验

- 汉明码采用分组校验

提高访存速度的措施

- 采用高速器件

- 采用层次结构 Cache-主存

- 调整主存结构

输入输出系统的组成

I/O软件

I/O指令(CPU指令的一部分)

格式:|操作码|命令码|设备码|

通道指令(通道自身的指令)

指出数组的首地址,传送字数。操作命令

I/O硬件

- 设备 I/O接口

- 设备 设备控制器 通道

I/O设备与主机的联系方式

统一编址(用取数,存数指令)

不统一编址(有专门的I/O指令)

联络方式

立即响应

异步工作采用应答信号(并行传输和串行传输)

I/O设备与主机的连接方式

辐射式连接(不便于增删设备)

总线连接(便于增删设备)

I/O设备与主机信息传送的控制方式

程序查询方式

程序中断方式

DMA方式

I/O接口

为什么要设置接口?

- 实现设备的选择

- 实现数据缓冲达到速度匹配

- 实现数据串-并格式转换

- 实现电平转换

- 传送控制命令

- 反映设备的状态

接口的功能和组成

| 功能 | 组成 |

|---|---|

| 选址功能 | 设备选择电路 |

| 传送命令的功能 | 命令寄存器,命令译码器 |

| 传送数据的功能 | 数据缓冲寄存器(DBR) |

| 反映设备状态的功能 | 设备状态标记 |

接口类型

按数据传送方式分类

并行接口(Intel 8255)

串行接口(Intel 8251)

按功能选择的灵活性分类

可编程接口(Intel 8255,Intel 8251)

不可编程接口(Intel 8212)

按通用性分类

- 通用接口(Intel 8255,Intel 8251)

- 专用接口(Intel 8279,Intel 8275)

按数据传送的控制方式分类

- 中断方式(Intel 8259)

- DMA接口(Intel 8257)